## **SESSION**

## PROCESSOR and INTEGRATED CIRCUIT DESIGN + LOW POWER COMPUTING + TESTING

Chair(s)

TBA

## Allocation of NBTI Aging Sensors for Circuit Failure Prediction

## Samir Mahaboob Khan Kagadkar and Hussain Al-Asaad

Department of Electrical and Computer Engineering, University of California, Davis

**Abstract**—Negative bias temperature instability (NBTI) is a critical device reliability concern in nanometer-scale CMOS processes. We review the degradation effects of this phenomenon and present techniques to measure and combat NBTI aging. Such techniques involve the insertion of specialized aging sensors and their use in self-correcting dynamic reliability management systems. We propose a novel approach to optimize the allocation of such aging sensors to minimize overhead.

**Keywords:** Integrated Circuit (IC) reliability, Circuit failure prediction, Negative Bias Temperature Instability (NBTI)

## 1. Introduction

Engineers working on the design of modern integrated circuits (ICs) fabricated in nanometer-scale technologies are in the unenviable position of having to face a plethora of issues that were benign in the past. Mounting parametric variability, radiation-induced soft errors and time-dependent device degradation make transistors increasingly unreliable components. A generation of engineers is realizing that hardware failures from these unreliable components are a distinctly realistic possibility.

Phenomena such as negative bias temperature instability, hot carrier injection, dielectric breakdown and electromigration limit circuit lifetimes. These degradation mechanisms are only increased with future technology scaling, further exacerbating an already diminished reliability. As Moore's Law packs more transistors on each chip, it is essential to design robust systems that can cope with these and other unexpected challenges.

Negative Bias Temperature Instability (NBTI) is a progressive aging phenomenon that results in reduced circuit performance. It occurs in p-channel MOS (pMOS) transistors that are stressed by negative gate voltages and elevated temperatures. NBTI has been recognized as a leading parametric failure mechanism in modern nanometer-scale ICs [1], [2].

Traditionally all parametric variations and aging effects have been tested via a go/no-go stress qualification methodology. ICs are designed to withstand a sustained combination of worst-case voltages, temperatures and parametric variation. Aging effects have been similarly factored in via their worst-case contribution to reliability degradation. As variability and degradation mechanisms worsen on modern fabrication processes, these worst-case guardbands are becoming increasingly pessimistic and resulting in lost performance and energy-efficiency.

An alternate approach is dynamic reliability management which uses specialized on-chip measurement circuitry to track variation and aging. Inputs from aging sensors and a history of past conditions predict future degradation and help optimize circuit tuning parameters such as voltage and frequency to prolong lifetimes. By minimizing pessimistic guardbands, such ICs offer optimal performances-per-joule of energy spent.

We first review the mechanisms behind and effects of NBTI degradation. We introduce sensors that track aging effects and their role in reliability management systems. In particular we explore a strategy that results in an economical allocation of aging sensors. An optimal allocation of aging sensors results in lower overhead and, hopefully, will hasten adoption of circuit failure prediction sensing in ICs.

# **2. Review of NBTI: Device-level and Circuit-level Effects**

The phenomenon of NBTI occurs in p-channel MOS-FET devices (pMOS) which are stressed with negative gate voltages at elevated temperatures. Although either negative voltages or elevated temperatures can cause NBTI, the effect is most strongly manifested when these conditions occur together. At a transistor level NBTI exhibits itself as decreases in absolute drain current  $I_{DSat}$ , transconductance  $g_m$  and absolute "off" current  $I_{off}$ , and increases in threshold voltage  $|V_T|$  ( $V_T$  becomes more negative). At a digital circuit level, the increased pMOS threshold voltages and degraded drive current capabilities result in reduced performances and timing shifts. These timing shifts can eventually lead to delay faults and device failures.

Typical stress conditions are temperatures of  $100-250^{\circ}$ C and oxide electric fields of a few MV/cm. Elevated temperatures and high electric fields have become common in modern IC operation, especially when processing heavy workloads.

Various mechanisms have been described to explain the physics of NBTI. One theory that is commonly suggested is the breaking of Si-H bonds at the silicon/oxide interface resulting in the generation of dangling Si bonds. These dangling bonds act as electrically active interface traps. Under NBTI stresses, these traps are usually positively charged and result in threshold voltage increases. Details of such mechanisms can be found in [3].

Knowledge of NBTI dates as far back as the 1960s and 1970s [4], [5]. These early experiments established the buildup of positive charges at the interface  $Q_{it}$  due to NBTI, sensitivity of these charges to temperature as well as a power law dependence on aging times ( $t^{0.25}$ ).

Commonly used surface channel MOSFET devices with SiO<sub>2</sub>-based gate dielectric exhibit the NBTI effect. With each technology generation, more and more high-performing devices are being packed onto single dies. Such high densities and rapid switching have increased on-die temperatures ( $T \approx 100^{\circ}$ C), especially at peak activity. The non-linear reduction of operating voltages with the technology scaling has resulted in high gate oxide electric fields. The shift to nitrided oxides on advanced CMOS devices aggravated the NBTI effects. Moreover the interface trap density introduced by NBTI has a  $1/t_{\rm ox}$  dependence on the oxide thickness  $t_{\rm ox}$ , making the effect more pronounced on modern, ultra-thin gate oxide CMOS devices.

More recent MOS processes at the 45n and below technology nodes introduced high-k dielectrics and metal gates to combat high levels of leakage from ultra-thin SiON dielectrics. Such devices also exhibit bias temperature instability [2].

## 2.1 Interface States and Device-level Characteristics of NBTI Damage

The threshold voltage of a p-channel MOSFET device is given by [6]:

$$V_T = V_{\rm FB} - 2\psi_{Bn} - \frac{|Q_s|}{C_{\rm ox}} \tag{1}$$

The second term is the surface potential at strong inversion  $\psi_s \approx -2\psi_{Bn} = -2\ln(N_D/n_i)$ .  $|Q_s| = \sqrt{2\epsilon_s q N_D(2|\psi_{Bn}|)}$  represents total space charge density.  $V_{\rm FB}$  is the flatband voltage and is given by:

$$V_{\rm FB} = \phi_{\rm ms} - \frac{Q_f}{C_{\rm ox}} - \frac{Q_{\rm it}}{C_{\rm ox}}$$

(2)

Here  $\phi_{\rm ms}$  is the work function difference between the metal and semiconductor.  $Q_f$  and  $Q_{\rm it}$  are densities of fixed charge and interface traps respectively.  $N_D$  is substrate doping density.  $C_{\rm ox}$  is the oxide capacitance per unit area. The other symbols have the usual meanings.

An interface trapped charge, also called an interface trap, is a dangling bond at the  $SiO_2/Si$  interface. These interface traps are electrically active defects that can act as generation/recombination sites. Since electrons and holes occupy the trap states, they contribute to threshold voltage shifts:

$$\Delta V_T = -\Delta Q_{\rm it} / C_{\rm ox} \tag{3}$$

Interface traps have energy states that are distributed throughout the forbidden gap, acting as acceptors in the upper half and donors in the lower half. In pMOS devices under inversion, NBTI stress leads to an activation of positively charged interface traps. This results in the threshold voltage becoming more negative (increase in  $|V_T|$ ).

NBTI causes degradation in device characteristics and reduced performance. The MOSFET saturation drain current and transconductance are:

$$I_{\rm DSat} = (W/2L)\mu_{\rm eff}C_{\rm ox}(V_G - V_T)^2$$

(4)

$$g_m = (W/L)\mu_{\text{eff}}C_{\text{ox}}(V_G - V_T)$$

(5)

The threshold voltage changes described above result in reduced gate overdrive  $(V_G - V_T)$  and hence degraded drive currents and device transconductances.

# 2.2 Circuit-level Characteristics of NBTI Damage

Studies have shown that pMOS threshold voltages can shift by 50 mV over a period of ten years. The associated drive current reduction and lower device performance translates to over 20% degradation in circuit speed [3], [7].

Negative gate bias stresses correspond to the "output high" state of the CMOS inverter operation. With speedy transition times on high performance circuits, large portions of time can be spent in the NBTI stress state. Such stresses may be coupled with high temperatures depending on device workloads and position on the die. High activity regions of the IC often reach elevated temperatures.

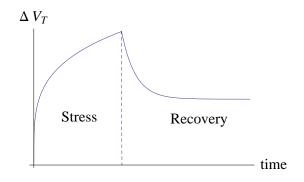

NBTI has been shown to be a dynamic phenomenon [1]. A large fraction of the interface traps activated under the NBTI stressing are annealed when the CMOS inverter switches to a "low" output state. This recovery phase may be explained by the diffusion of hydrogen back into the  $Si/SiO_2$  interface thus passivating interface traps. Figure 1 illustrates threshold voltage degradation during negative bias stress and subsequent recovery under positive bias. The temperature sensitivity and the dynamic nature of NBTI degradation make the phenomenon strongly dependent on the actual computational workloads of the IC.

Fig. 1: pMOS NBTI vs. time illustrating both degradation and recovery when stress is removed. Note that magnitude of threshold voltage is used here.

The reduced drive characteristics and circuit speed result in delay shifts of timing paths that contain NBTI damaged gates. These delay shifts may or may not immediately manifest themselves as delay faults. For example, a timing path may possess more timing margin (slack before the onset of degradation) than the delay degradation caused by NBTI. These delay shifts can be used as indicators of NBTI, and sensors based on this principle are explored in sections ahead.

## 3. Combating Aging

An ideal solution to limit aging and the associated parametric degradation is to improve device fabrication process. Improved passivation of interface trap states reduces the NBTI effect. As process scaling is approaching physical and manufacturing limits, radical process improvements are nontrivial. A design engineer must recognize that aging is a realistic concern that must be dealt with proactively. Such design techniques are explored in this section.

#### 3.1 Guardbands

This involves estimating the cumulative worst-case degradation that may occur over the lifetime of a device due to a combination of temperature, voltage, computing workload and other stresses. The clock frequency is reduced to accommodate for this worst-case degradation.

#### 3.2 Dynamic Reliability Management

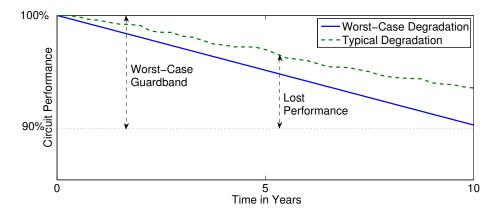

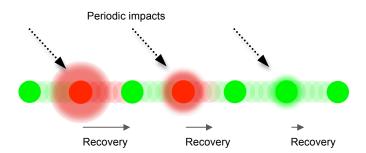

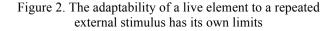

The technique of guardbands is based upon continuous stressing of a sample under pessimistic operating conditions and evaluating whether it passes or fails. In reality widely varying operation conditions and dynamic power saving methods mean most parts are not stressed to these worstcase levels. Thus by using pessimistic guardbands, we lose out on a substantial performance margin between worst-case conditions and typical conditions. This loss is illustrated in Figure 2.

An alternate approach to worst-case stress qualification is a knowledge-based risk assessment and mitigation technique. A framework for application-specific knowledge-based test is defined by the JEDEC JESD-94 standard [8]. This requires a detailed knowledge of individual failure mechanisms and their models. Tests are developed to capture these failure modes under a range of operation conditions and reliability targets specific to the device's end use and application. Implementations of this knowledge-based approach are often termed as dynamic reliability management [9], [10].

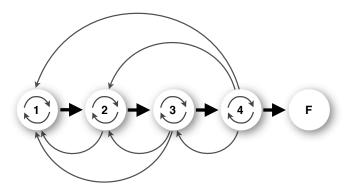

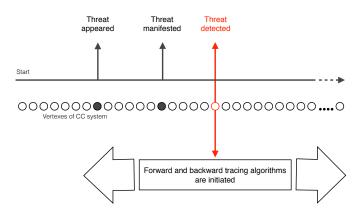

The dynamic reliability management system we envisage uses real-time on-die measurements including voltage, thermal information, computing workloads and inputs from specialized on-die aging sensors. Characterization and analysis of failure mechanisms provides models that can use these inputs and past operating history to predict future degradation. These predictions allow the adjustment of circuit control parameters as a self-correcting measure to guarantee the device is under a reasonable reliability envelope.

#### **3.3 Self-Correction**

Dynamic Voltage Frequency Scaling (DVFS) is the scaling of clock frequency and/or supply voltage dynamically and has been used to trade-off between a device's time-dependent performance and its energy consumption. At peak demand, both voltage and frequency can be scaled up to guarantee maximum performance. On the other hand these can be reduced at periods of low activity, thus ensuring low average power consumption. Since voltage scaling helps offset delay degradation on aged timing paths, this can be used to correct for NBTI degradation [11], [12].

It must be noted that higher supply voltages ( $V_{DD}$ ) tend to increase the rate of NBTI degradation. Thus it is important to carefully choose supply voltages that do not unnecessarily accelerate aging effects if such voltage increases are not immediately required. Moreover higher voltages also cause increased power consumption and the associated rise in operating temperature that further exacerbates NBTI aging.

Since bias temperature instability causes increases in threshold voltage, this results in reduced subthreshold currents and a corresponding reduction in total circuit leakage power ( $I_{\rm sub} \propto e^{\frac{-V_T}{mkT}}$ ). This presents us an opportunity of trading off this power saving for recovered performance by forward body biasing (FBB) the devices [13], [14].

A combination of the adaptive voltage scaling and adaptive body bias techniques can be used to correct for aging wearout. This correction scheme is embedded as part of a more general circuit tuning framework which dynamically matches operating voltage, frequency and body bias to application-based performance needs, power saving goals, and to combat variations in process and temperature.

## 4. Aging Sensors

Real-time chip- and system-level sensors measure and track the actual aging process and allow the implementation of reliability enhancement processes that can compensate for aging effects. The insertion of such sensors as part of a larger self-correcting dynamic reliability management system is one way to avoid overly pessimistic design margins.

Most modern high performance ICs already include onchip measurement circuits such as process monitors (for example, ring oscillators) and temperature sensors. It is probably unwise to rely solely on the inputs from such conventional monitor cells [15]. Due to the time and location variability of stresses from dynamic workloads, the stresses faced by a conventional monitor might be very different from the stresses faced by various functional modules of the chip.

NBTI degradation manifests itself in a number of visible ways. Any of these signatures can be measured by specialized aging sensors and used to detect NBTI-based

Fig. 2: Reliability degradation over time

circuit aging. Most commonly degradation in circuit speed is measured to detect NBTI. Data collected from these aging sensors is supplanted with data from conventional measurement circuits (thermal and voltage monitors) and data logs (operating history, sleep states and past measurements from on-die sensors). This information can be used to predict future reliability failures.

Some techniques for designing NBTI sensors include analog measurements. Measurement of quiescent power supply current ( $I_{DDQ}$  test) [16] or measurement of the control voltage for locking a delay-locked-loop [17] are examples of such techniques. Several other groups have suggested the use of ring oscillators to track NBTI aging [18], [19], [20]. In practice the use of analog measurements is unwieldy for measurement of in-field aging. Moreover, it is uncertain that the wearout of ring oscillator elements occurs at the same rate as data-dependent aging on paths in functional modules.

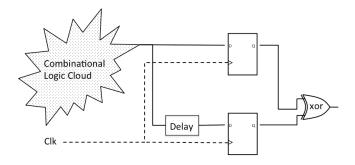

Agarwal et al. developed an NBTI measurement technique that embeds delay shift measuring circuitry within existing design flip-flops [15]. Their essential idea is to compare a delayed sample of the signal at the input of a flip-flop with the original sample. Figure 3 illustrates this idea.

Fig. 3: Measurement circuitry that compares original and delayed samples indicating guardband violation. Adapted from [15].

They define a guardband interval as a small worst-case timing guardband that ensures circuit functionality over a short period of time, for example fifteen days. The design is closed with this safety margin and thus is ensured to work over the period of the guardband interval. Data at the output of logic cones is double sampled. A regular flip-flop takes one sample of the data and another flip-flop samples the data after a specified delay. This timing shift is implemented by a delay element with a delay equal to the guardband interval. These sampled signals are now compared via an exclusive-OR (XOR) gate. If the compared signals differ, this results in a logic-high signal at the output of the XOR gate. This indicates at least one timing path in the combinational logic cloud has sufficiently degraded due to aging thus entering the guardband and further timing degradation might cause a delay fault. If this has happened the IC enters a selfcorrection phase where guardbands and system parameters are adjusted to ensure future reliability [21]. Related research uses the general principle but has different circuitry of the sensor [15]. By sampling critical functional timing paths, these sensors measure in-situ aging due to real computing workloads of the device. We will consider this technique as the sensor of choice for future sections.

## 5. Allocation of Aging Sensors

In this section we explore a methodology to place NBTI aging sensors. A frugal insertion strategy minimizes overhead of these sensors. The insertion of aging sensors comes at the cost of area and power. For example, the sensors described earlier double sample logic outputs. The additional flip-flops add an area overhead as well as consume power when they sample data. Moreover signals from the aging sensors need to be routed to a dynamic reliability management unit for analysis which causes wiring overhead.

Since dynamic NBTI exhibits both stress and recovery (passivation) phases during circuit operation, the degradation due to NBTI is sensitive to the input patterns applied. In addition to voltage and temperature information, estimates of delay shifts should consider node switching activities from realistic computational workloads. NBTI degradation models that include activity factors indicating the fraction of time spent in stress states are presented in [22], [23]. Circuit topologies and realtime workloads cause duty cycles that vary both spatially and temporally and between gates within a logic cone.

Furthermore, dynamic on-die temperature readings are very workload dependent and temperature hotspots for one application might differ significantly from the temperature hotspots for another application. It is thus important to develop and use a well-representative mix of benchmark applications that will model realistic in-field computing workloads and temperature stresses generated therein. In addition to data-dependence, thermal profiles depend on the power-saving options in use on the device. Measures such as power gating, clock gating and other sleep states can cause large variations in temperature maps.

## 5.1 Optimal Placement of NBTI Aging Sensors

A naïve strategy for insertion is to place them at all flipflops where setup timing slack is less than our guardband interval [24]. This aging estimate is based on static NBTI and is hence unnecessarily pessimistic. Agarwal et al. improve upon this strategy by performing timing analysis assuming a worst-case activity factor of 0.95 (fraction of time spent in pMOS stress state). In our opinion the overhead obtained with this empirical activity ratio is still too high for practical use on ICs. For example their analysis requires embedding aging sensors on a particularly large number of flip-flops. On two designs they report 16% and 52% of flip-flops that need embedding of aging sensors [24]. Another important consideration that is not considered explicitly in their work is the impact of thermal stress.

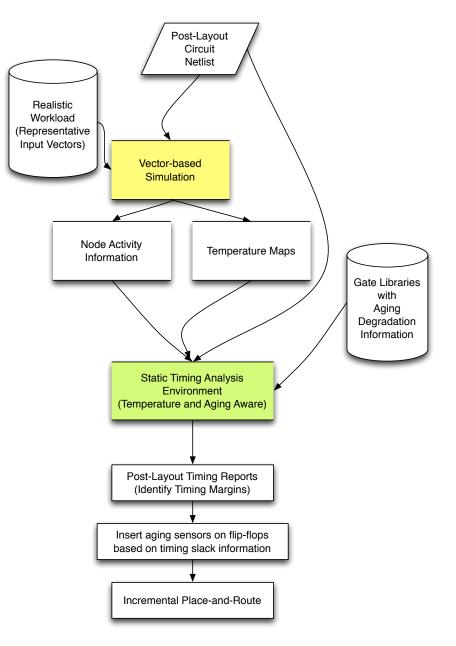

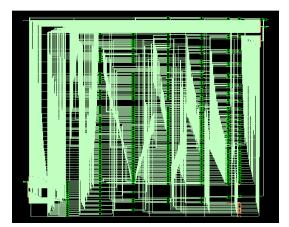

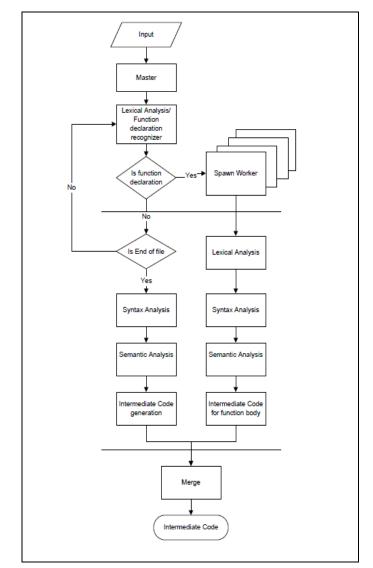

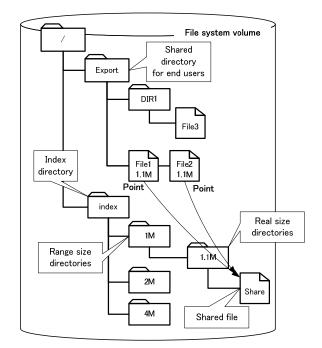

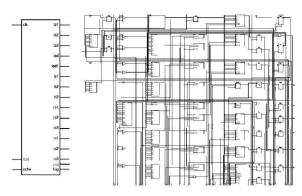

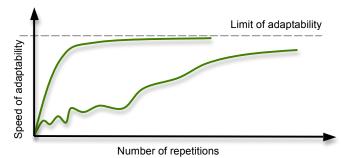

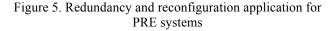

We propose an alternate strategy that minimizes the overhead of on-chip aging sensors by including the realistic considerations of activity ratios and temperature profiles. Timing analysis is performed on post-layout netlists as a part of design closure to ensure correctness of device operation under specified performance targets. This analysis is often performed using a static timing analysis (STA) tool such as Synopsys PrimeTime. Our strategy to decide optimal locations for aging sensors is only a simple modification to an existing STA flow.

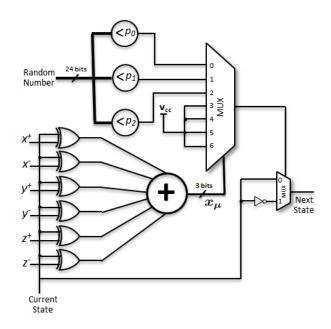

This strategy is outlined in Figure 4. Multiple vector based simulations are performed on the circuit netlist for a mix of representative real-world workloads. Such analysis is often performed on post-layout netlists to obtain dynamic power and dynamic voltage drop estimates. This simulation yields application-specific node activity information as well as temperature maps. Temperature maps could also be obtained by a separate analysis or based on previous silicon measurements. These activity and temperature maps are overlaid on the static timing analysis (STA) environment. An aging aware cell library embeds cell-level aging information specific to activity ratios at gate inputs and operating temperature. Timing slacks obtained from such applicationspecific timing analyses allows insertion of aging sensors optimally. Flip-flops with timing slack less than a specified guardband interval are most sensitive to NBTI aging and its associated slowdown. These are now replaced by flip-flops with aging sensors embedded within them.

Our STA flows can be sped up by eliminating non-critical end-points from our analysis. Timing paths with enough slack to tolerate pessimistic degradation can be skipped from the detailed temperature-sensitive and vector-based timing analysis. For example, end-points with more setup slacks than would be lost under worst-case static NBTI degradation at elevated temperatures are eliminated from our analysis.

Once critical end-points are identified by timing analysis, we insert aging sensors at these locations and perform incremental place-and-route to obtain final layouts. By inserting sensors on paths that are most sensitive to aging, we are able to minimize the overhead of aging sensors.

## 6. Conclusion

NBTI is a phenomenon that contributes significantly to reduced reliability of pMOS transistors and ICs that use these transistors as building blocks. Although we are not yet facing an insurmountable barrier due to such issues, additional complexity has been introduced on already burdened engineers. Design engineers can use measurements of in-field aging by the use of specialized on-die measurement circuits. These measurements are used to predict future circuit failures and also used in a dynamic reliability management framework to tune circuit control parameters such as voltage and body bias. We reviewed aging sensors that track NBTI degradation and explored a strategy based on application-specific data for the economical allocation of such sensors.

Fig. 4: Flow to optimally insert aging sensors

## References

- G. Chen, M. Li, C. Ang, J. Zheng, and D. Kwong. "Dynamic NBTI of p-MOS transistors and its impact on MOSFET scaling." In: *Electron Device Letters*, *IEEE* 23.12 (2002), pp. 734–736.

- [2] J. Hicks, D. Bergstrom, M. Hattendorf, J. Jopling, J. Maiz, S. Pae, C. Prasad, and J. Wiedemer. "45nm transistor reliability." In: *Intel Technology Journal* 12.2 (2008), pp. 131–144.

- [3] D. Schroder and J. Babcock. "Negative bias temperature instability: Road to cross in deep submicron

silicon semiconductor manufacturing." In: *Journal of Applied Physics* 94.1 (2003), pp. 1–18.

- [4] B. Deal, M. Sklar, A. Grove, and E. Snow. "Characteristics of the Surface-State Charge (Qss) of Thermally Oxidized Silicon." In: *Journal of the Electrochemical Society* 114.3 (1967), pp. 266–274.

- [5] A. Goetzberger, A. Lopez, and R. Strain. "On the Formation of Surface States during Stress Aging of Thermal Si-SiO2 Interfaces." In: *Journal of the Electrochemical Society* 120.1 (1973), pp. 90–96.

- [6] S. Sze and K. Ng. *Physics of semiconductor devices*. Wiley-interscience, 2006.

- S. Borkar. "Electronics beyond nano-scale CMOS." In: Proceedings of the 43rd annual Design Automation Conference. ACM. 2006, pp. 807–808.

- [8] J. JESD94A. "Application Specific Qualification Using Knowledge Based Test Methodology." In: JEDEC Solid State Technology Association (2007).

- [9] E. Karl, D. Blaauw, D. Sylvester, and T. Mudge. "Multi-mechanism reliability modeling and management in dynamic systems." In: Very Large Scale Integration (VLSI) Systems, IEEE Transactions on 16.4 (2008), pp. 476–487.

- J. Srinivasan, S. Adve, P. Bose, and J. Rivers. "The case for lifetime reliability-aware microprocessors." In: ACM SIGARCH Computer Architecture News. Vol. 32. 2. IEEE Computer Society. 2004, p. 276.

- [11] L. Zhang and R. P. Dick. "Scheduled voltage scaling for increasing lifetime in the presence of NBTI." In: *Design Automation Conference*, 2009. ASP-DAC 2009. Asia and South Pacific. IEEE. 2009, pp. 492– 497.

- [12] A. Tiwari and J. Torrellas. "Facelift: Hiding and slowing down aging in multicores." In: *Microarchitecture*, 2008. MICRO-41. 2008 41st IEEE/ACM International Symposium on. IEEE. 2008, pp. 129–140.

- [13] J. W. Tschanz, J. T. Kao, S. G. Narendra, R. Nair, D. A. Antoniadis, A. P. Chandrakasan, and V. De. "Adaptive body bias for reducing impacts of die-to-die and within-die parameter variations on microprocessor frequency and leakage." In: *Solid-State Circuits, IEEE Journal of* 37.11 (2002), pp. 1396–1402.

- [14] S. V. Kumar, C. H. Kim, and S. S. Sapatnekar. "Adaptive techniques for overcoming performance degradation due to aging in digital circuits." In: *Proceedings* of the 2009 Asia and South Pacific Design Automation Conference. IEEE Press. 2009, pp. 284–289.

- [15] M. Agarwal, B. Paul, M. Zhang, and S. Mitra. "Circuit failure prediction and its application to transistor aging." In: VLSI Test Symposium, 2007. 25th IEEE. IEEE. 2007, pp. 277–286.

- [16] K. Kang, K. Kim, A. Islam, M. Alam, and K. Roy. "Characterization and estimation of circuit reliability degradation under NBTI using on-line IDDQ measurement." In: *Design Automation Conference*, 2007. DAC'07. 44th ACM / IEEE. IEEE. 2007, pp. 358–363.

- [17] J. Keane, T. Kim, and C. Kim. "An on-chip NBTI sensor for measuring PMOS threshold voltage degradation." In: Very Large Scale Integration (VLSI) Systems, IEEE Transactions on 18.6 (2010), pp. 947–956.

- [18] V. Reddy, A. Krishnan, A. Marshall, J. Rodriguez, S. Natarajan, T. Rost, and S. Krishnan. "Impact of negative bias temperature instability on digital circuit reliability." In: *Microelectronics Reliability* 45.1 (2005), pp. 31–38.

- [19] T. Kim, R. Persaud, and C. Kim. "Silicon odometer: An on-chip reliability monitor for measuring frequency degradation of digital circuits." In: *Solid-State Circuits, IEEE Journal of* 43.4 (2008), pp. 874–880.

- [20] E. Karl, P. Singh, D. Blaauw, and D. Sylvester. "Compact in-situ sensors for monitoring negativebias-temperature-instability effect and oxide degradation." In: Solid-State Circuits Conference, 2008. ISSCC 2008. Digest of Technical Papers. IEEE International. IEEE. 2008, pp. 410–623.

- [21] Y. Li, Y. Kim, E. Mintarno, D. Gardner, and S. Mitra. "Overcoming early-life failure and aging for robust systems." In: *Design & Test of Computers, IEEE* 26.6 (2009), pp. 28–39.

- [22] S. Bhardwaj, W. Wang, R. Vattikonda, Y. Cao, and S. Vrudhula. "Predictive modeling of the NBTI effect for reliable design." In: *Custom Integrated Circuits Conference, 2006. CICC'06. IEEE.* IEEE. 2006, pp. 189–192.

- [23] W. Wang, S. Yang, S. Bhardwaj, R. Vattikonda, S. Vrudhula, F. Liu, and Y. Cao. "The impact of NBTI on the performance of combinational and sequential circuits." In: *Design Automation Conference*, 2007. DAC'07. 44th ACM/IEEE. IEEE. 2007, pp. 364–369.

- [24] M. Agarwal, V. Balakrishnan, A. Bhuyan, K. Kim, B. C. Paul, W. Wang, B. Yang, Y. Cao, and S. Mitra. "Optimized circuit failure prediction for aging: Practicality and promise." In: *Test Conference, 2008. ITC 2008. IEEE International.* IEEE. 2008, pp. 1–10.

# Implementation of a Fast Fourier Transform Processor in NULL Convention Logic

Zhen Song and Scott C. Smith

Department of Electrical Engineering, University of Arkansas, Fayetteville, AR, U.S.A. szuark@gmail.com and smithsco@uark.edu

**Abstract** – The Fast Fourier Transform (FFT) is a critical part in communication systems, because it can greatly reduce the computation requirement for signal processing. This paper presents the design of a FFT processor using NULL Convention Logic (NCL), which has been shown to have power consumption advantages over its synchronous counterpart. Performance metrics for the NCL FFT processor are obtained from Cadence simulation, and compared to an equivalent synchronous implementation.

#### 1. INTRODUCTION

Hardware implementations of FFT are divided into two categories, fixed-point and floating-point. Although floating-point numbers inherently have large dynamic range, hardware implementation is larger, slower, and more power consuming than the fixed-point counterpart. This is because arithmetic operations for both mantissa and exponent need to be handled in the hardware [1]. Therefore, in order to design a low-power and high-speed processor, a synchronous FFT processor is usually designed using Q15 Fixed-point format [1, 2].

#### 2. PREVIOUS WORK

#### 1) Synchornous FFT Architecture:

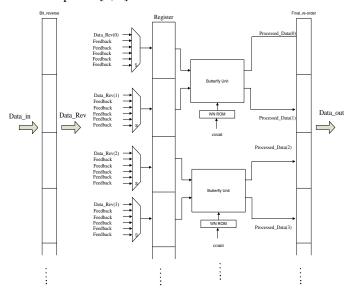

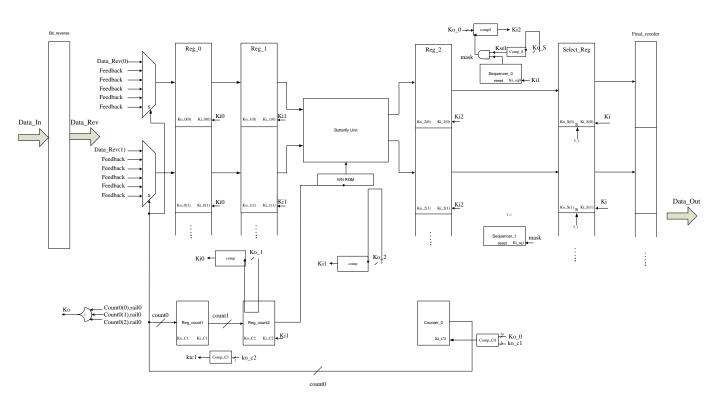

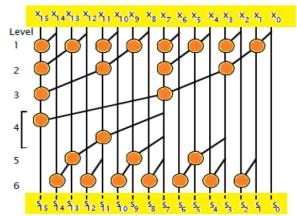

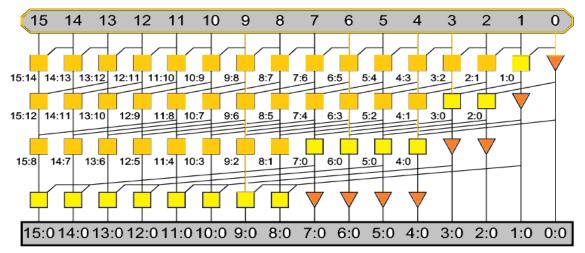

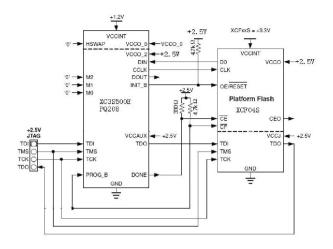

The synchronous FFT processor in Figure 1 utilizes a single stage architecture. 32 butterfly units are used, one for each two points [4, 5].

Figure 1. Synchronous FFT architecture

The feedback from each stage is hardcoded on MUX inputs. The select signal on the MUX is controlled by a counter, which counts the computation stages. A 64-point FFT requires 6 butterfly computation stages, so computing one set of input data will take 6 clock cycles. As shown in Figure 1, the 64-bit Data in first goes through the Bit reverse unit to get bit-reverse ordered Data\_Rev. Then, for the first stage, each butterfly unit gets two points and calculates the corresponding intermediate results, called Processed Data. These intermediate data are then fed back to the multiplexers for computations in the next stage. The MUXs take in Processed\_Data from the previous stage as input for computation on the current stage. This kind of data flow continues until the final computation stage. After calculations in the final stage, a final re-order unit is used to output data in the correct order.

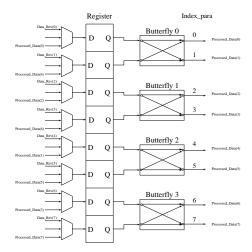

Figure 2. Hardcoded MUX inputs of 8-bit FFT

The calculation of MUX index is presented as follows [3]: in the flow graph of FFT, butterflies cross over each other in an ascending manner in each stage. The index\_para for both inputs and outputs of butterfly0 are 0 and 1, 2 and 3 for butterfly1, and so on. For each node on both the right side and the left side of the butterfly groups in each stage, index\_cross is used. Index\_cross is the natural order we count from the first node all the way to the last node, from 1 to 64. Using excel, we can get corresponding relations to transfer index\_cross to index\_para on each stage and vice versa. The function to transfer index\_cross to index\_para on stage i is called CtoPi and the function to transfer index\_para to index\_cross on stage i is called PtoCi. In order to re-arrange the output of butterflies at stage i, the following equation is used:

#### CtoPi(PtoCi-1(index\_para))

Using the equations presented, the hardcoded MUX inputs of an 8-bit FFT are shown in Figure 2.

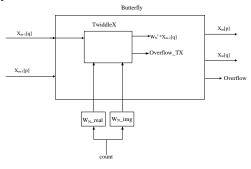

#### 2) Butterfly Unit

The butterfly unit in Figure 3 computes the following equations [4, 5].:

$$X_{m}[p] = X_{m-1}[p] + W_{N}^{r} X_{m-1}[q]$$

$X_{m}[q] = X_{m-1}[p] - W_{N}^{r} X_{m-1}[q]$

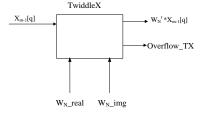

The twiddle factor multiplier, TwiddleX, as shown in Figure 4, calculates the complex multiplication of  $W_N^r X_{m-1}[q]$  inside the butterfly unit.

Figure 3. Butterfly unit

TwiddleX gets the value of  $W_{N_{-}}$  real and  $W_{N_{-}}$  img from a ROM, and calculates the following equation for complex multiplication:

$(Xr+j*Xi)*(W_{N}real+j*W_{N}img) = (Xr*W_{N}real-Xi*)$

$W_{N}img$ ) + j\*(Xi\*  $W_{N}real$  + Xr\*  $W_{N}img$ )

where Xr and Xi are the real and imaginary part of  $X_{m-1}[q]$

Figure 4. Twiddle factor multiplier

Each butterfly performs only 6 calculations for the entire process, so we only need to store the 6 specific  $W_N$  values in each ROM. Each addition and subtraction in the twiddle factor multiplier and the butterfly unit may cause overflow, so all overflow detection signals for these operations are combined together to get the final overflow signal at the output of the butterfly unit.

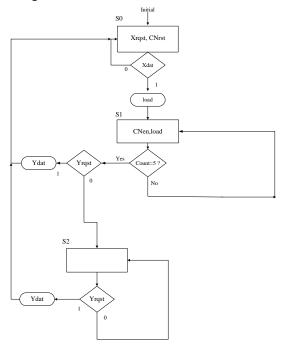

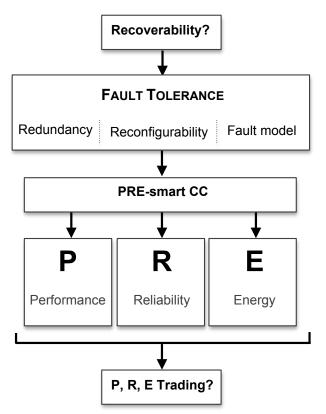

A 3-bit up-counter is used to control the FFT data path. This counter is reset to 0, and counts up whenever Enable is 1. The corresponding algorithmic state machine diagram is shown in Figure 5.

Figure 5. State machine diagram

Upon initialization, *Xrqst* is asserted to request new data, and counter is reset to 0. If *Xdat* is 1 the registers will load in the new data; otherwise they wait until *Xdat* is 1. In S1, FFT loads and calculates intermediate data until the count reaches 5. S2 is an idle state that is used to wait for *Yrqst* to be asserted before asserting *Ydat* to signify that the output is valid.

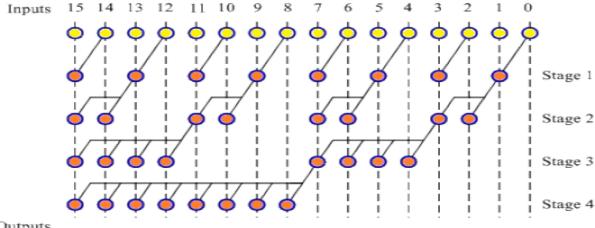

#### 3) Introduction to NCL

Generally, asynchronous circuits fall into one of two categories: bounded-delay model or delay-insensitive model. NCL circuits belong to the delay-insensitive model, which means they can operate correctly with little timing analysis [6, 7, 8]. Symbolic completeness of expression is utilized in NCL to realize delay-insensitivity. Specifically, dual-rail and quadrail logic are used in NCL design. Symbolically complete means that the outputs are only determined by the presence of the input signals, regardless of the timing relationship between the input signals [8].

In NCL, both dual-rail and quad-rail signals use space optimal 1-hot encoding and represent 1 bit by two wires [6, 7]. A dual-rail signal D consists of two wires:  $D^0$  and  $D^1$ , whose values are from the set {DATA0, DATA1, NULL}. DATA0 corresponds to logic 0 in Boolean logic, with  $D^0=1$  and  $D^1=0$ , while DATA1 is equivalent to logic 1 in Boolean logic, with  $D^0=0$  and  $D^1=1$ . NULL means the dual-rail signal is not available, so  $D^0 = 0$  and  $D^1=0$ . Just as logic 0 and logic 1 are mutually exclusive in Boolean logic, DATA0 and DATA1 are also mutually exclusive; therefore,  $D^0$  and  $D^1$  cannot be 1 simultaneously, which is defined as an illegal state. Similarly, a quad-rail signal uses 4 wires,  $D^0$ ,  $D^1$ ,  $D^2$ , and  $D^3$ , which can have a value of {DATA0, DATA1, DATA2, DATA3, NULL}. A quad-rail signal corresponds to two Boolean logic signals, X and Y. DATA0 is represented with  $D^0=1$ ,  $D^1=0$ ,  $D^2=0$ , and  $D^3=0$ , which corresponds to X=0 and Y=0. DATA1 is represented with  $D^1=1$  and the rest of the rails 0, which corresponds to X=0 and Y=1. DATA2 is expressed as  $D^2=1$ and the rest of the rails are 0, which corresponds to X=1 and Y=0. DATA3 is expressed as  $D^3=1$  and the rest of the rails are 0, which corresponds to X=1 and Y=1. NULL means the data is not available, so all four rails are 0. The four wires of a quad-rail signal are mutually exclusive, which means only one of them can be asserted at a time. If more than one rail is asserted, this state is defined as an illegal state [6, 9, 12, 13].

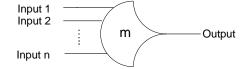

NCL logic is composed of 27 fundamental gates. Each rail in NCL logic, both dual-rail and quad-rail, counts as a separate variable. Each of the fundamental gates can have four or fewer variables as inputs. NCL gates are a subclass of the C-element. A C-element output assumes the value of the inputs when all inputs have the same value. Otherwise, the output remains its previous value [6]. The primary type of NCL gate is the THmn gate, where  $1 \le m \le n$ , as shown in Figure 6 [6, 10, 11].

Figure 6. THmn NCL Gate [6, 10, 11]

The THmn gate has n inputs and threshold of m. The output of the gate will only be asserted when at least m of the n inputs are asserted. The inputs are connected to the arc on the left-hand side. The output is connected from the tip on the right-hand side [6].

#### 3. NCL FFT PROCESSOR

#### 1) NCL Components

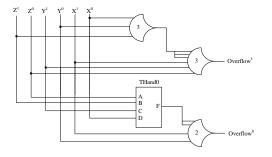

The NCL overflow detector is designed as shown in Figure 7.

Figure 7. NCL overflow detector

#### a) NCL Array Multiplier

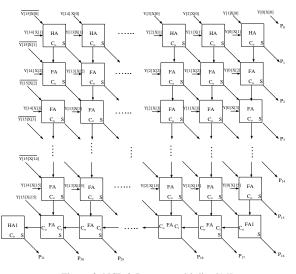

By using the Baugh and Wooley method [14], a 16-bit by 16-bit NCL array multiplier is designed, as shown in Figure 8. A partial product is generated by ANDing two bits of the input signal. Then some of the partial products are inverted according to the Baugh-Wooley scheme. In the array multiplier structure, adders only use wires to communicate to adjacent adders, thus making its layout area efficient.

Figure 8. NCL 2-D array multiplier [14]

#### b) NCL Counter

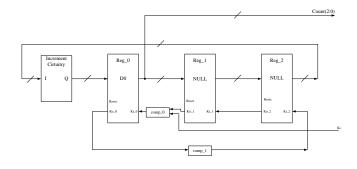

The NCL counter is comprised of increment circuitry and feedback registers. In order to prevent deadlock, at least three registers are needed in a feedback loop. The internal data flow is controlled by request signal  $K_i$  and acknowledge signal  $K_o$ . Completion detection circuits are used to detect complete DATA and NULL wavefronts [7]. The up counter with three feedback registers is shown in Figure 9.

Figure 9. NCL counter [7]

Reg0 is reset to DATA0 and Reg1 and Reg2 are reset to NULL, to allow the DATA-NULL wavefront flow. This counter is initially reset to DATA0; then it counts from 0 to 5 and is rolled over. The reset signal is a standard logic signal. As a result, there is no NCL input signal for the counter. Thus, no *Ko* signal is needed. The counter increment circuitry is shown in Figure 10.

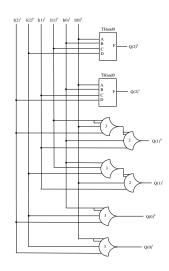

Figure 10. Counter increment circuitry

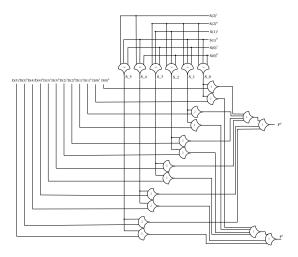

#### c) NCL 6 to 1 Multiplexer

In the FFT architecture, the inputs are only DATA at the beginning of the whole operation. The intermediate results then loop inside the FFT to compute the results. Therefore, the NCL multiplexer is designed to be input-incomplete with respect to the inputs, and only input-complete with respect to the select signal. Output F is DATA when select signal S is DATA and the selected input is DATA, and is NULL when S is NULL and the previously selected input is NULL. Internal control signals S\_0 through S\_5 are generated using TH33 gates, as shown in Figure 11.

Figure 11. NCL 6 to 1 MUX

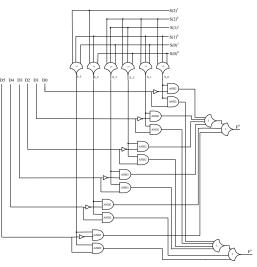

#### d) NCL Twiddle Factor Storage

Because the NCL circuit does not have an existing ROM, the twiddle factor values are stored using a multiplexer. The stored twiddle factor is in binary format. So, the MUX\_ROM is very similar to the NCL 6 to 1 MUX, except that the twiddle factor value is directly used as  $D^1$  and its inverse is used as  $D^0$ , as shown in Figure 12.

Figure 12. NCL multiplexer used as ROM

#### e) Sequence Generator

A sequence generator produces a specific stream of standard logic output using TH33 gates [9]. The sequence generator consists of a single-rail ring structure [15, 16].

For the NCL FFT, two sequence generators are needed that produce the following stream of bits, in order to only output the final FFT value by masking the output register's  $K_o$  during the internal iterations:

Table I. Sequence stream of Y\_0 and Y\_1

|       | Initial | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 |

|-------|---------|---|---|---|---|---|---|---|---|---|----|----|----|

| Reset | 1       | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  |

| Ki    | Х       | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0  | 1  | 0  |

| Y_0   | 1       | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0  | 1  | 1  |

| Y_1   | 0       | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 1  | 0  |

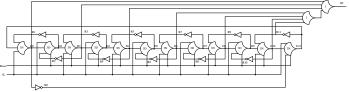

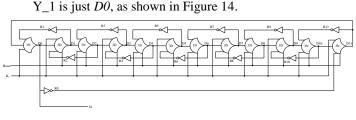

By observing the waveforms of internal nodes, Y\_0 is obtained by combining *D0*, *D2*, *D4*, *D6*, *D8*, *D10*, and *R11*, as shown in Figure 13.

Figure 13. Sequence generator for Y\_0

Figure 14. Sequence generator for Y\_1

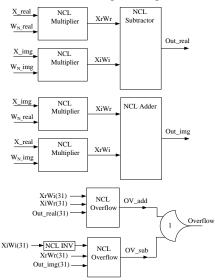

#### f) NCL Twiddle Factor Multiplier

The design for NCL twiddle factor multiplier is shown in Figure 15. The NCL overflow component is designed for addition. So, the sign bit of XiWi(31) resulting from the subtraction needs to be inverted before it enters the overflow component. The overflow signal from addition and subtraction are combined using TH12 gate.

Figure 15. NCL Twiddle Factor Multiplier

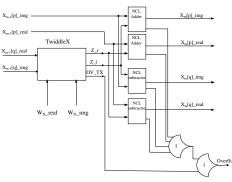

#### g) NCL Butterfly Unit

The design for the NCL butterfly unit is shown in Figure 16. The NCL overflow signals are combined using a TH14 and TH12 gate to get the final overflow signal.

Figure 16. NCL Butterfly Unit

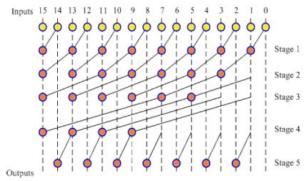

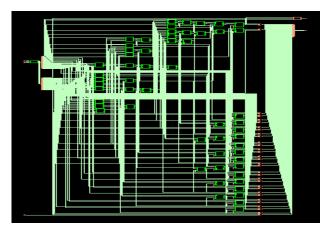

#### 2) NCL FFT Top-level Architecture

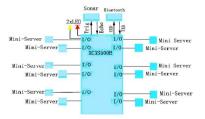

The NCL FFT utilizes a similar architecture as the synchronous one. In total, 32 butterfly units are used; one for each two points. For simplicity, only one butterfly unit is shown in Figure 17. It takes 6 DATA/NULL cycles to compute all 64 points. In each DATA/NULL cycle, the intermediate data is fed back to the multiplexer. The select signal of the multiplexer is controlled by a counter. Once the computation finishes, the final results are re-ordered before being output.

In NCL FFT logic, the  $X_{rqst}$ ,  $X_{dat}$ ,  $Y_{rqst}$ , and  $Y_{dat}$  signals are no longer needed since NCL circuits use  $K_i$  and  $K_o$  as request and acknowledge signals. The internal register of the synchronous FFT is replaced with 3-register NCL feedback to prevent deadlock. The NCL FFT architecture is shown in Figure 17.

Upon reset, all NCL registers are initialized to NULL. When Data\_in is ready, counter\_0 outputs 0 to select bitreversed new data to load into Reg 0. In the following 5 iterations, the intermediate results are fed back to Reg 0 through the multiplexer. In the  $6^{th}$  iteration, the final results are computed and loaded into Select\_Reg, and new data is loaded into Reg 0 at the same time. The Final reorder unit rearranges the sequence of results and outputs the final result. New data is loaded into NCL FFT every 6 iterations. Select Reg is connected to the external Ki signal and is reset to NULL at the beginning of each new FFT computation. During these iterations, Ko S from Select Reg is always requesting DATA. In order to let the internal data feedback through, the request signal from Select Reg needs to be masked for the first 5 iterations. An AND gate and Sequencer\_0 are used to realize this function. Request signal Ksel from select register is masked by an AND gate. As described in Section III.A, Y\_0 from sequencer 0 is asserted during cycles 1, 3, 5, 7, and 9. This stream of signal from Y\_0 mimics the requesting behavior of DATA/NULL wavefront from request register for the first 5 iterations. In the last iteration, Y\_1 is asserted to allow the final result to load into Select\_Reg. The request signal for Sequencer 0 is connected to the completion detection signal  $K_i l$  from Reg\_2. In addition, the select signal in Select Reg needs to be asserted to load data. Sequencer 1 is used to produce this signal.

Y\_1 from Sequence\_1 stays at 0 during the first 5 iterations and is asserted at cycle 11, which is the data cycle for the 6<sup>th</sup> iteration. The request signal for Sequencer\_1 is connected to the mask signal. As seen in Figure 17, data needs to propagate through Reg\_0 and Reg\_1 to arrive at the butterfly unit for computation. Two registers are used to latch the count value so that the corresponding twiddle factor value is loaded from ROM to do the computation. NCL FFT loads new data when the count is rolled over to 0, so the  $K_o$  signal is generated when count is 0. This is done by connecting count<sub>0</sub><sup>0</sup>, count<sub>1</sub><sup>0</sup> and count<sub>2</sub><sup>0</sup> to a TH33 gate.

Figure 17. NCL FFT architecture

#### 4. SIMULATION AND CONCLUSION

#### 1) Comparison of Results from NCL FFT and Matlab

The word length of Q15 format is 16 bits. Because of this finite bit-length, some least significant bits are truncated during FFT computation. This truncation error is accumulated in the feedback path. Compared with Matlab calculation results, in the worst case scenario, the last 3 bits from the NCL FFT computation are not accurate. There are 16 bits for each word, so the error rate for the NCL FFT is  $2^3/2^{16} = 0.012$  %.

#### 2) Performance of Synchronous FFT and NCL FFT

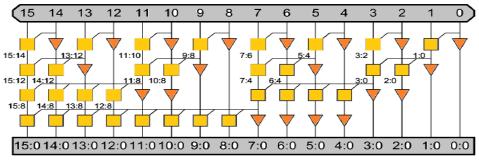

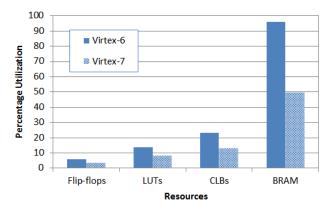

The synchronous FFT and NCL FFT are synthesized to the the IBM cmr8f 130nm process library. These synthesis results are listed in Table II, showing that the NCL FFT uses about four times as many transistors compared to the synchronous FFT.

Table II. Number of transistors used in synchronous and NCL FFT

|                 | Number of Transistors |

|-----------------|-----------------------|

| NCL FFT         | 4983104               |

| Synchronous FFT | 1335802               |

Power consumption and computation speed are simulated in Cadence, and shown in Table III. The average computation time for one complete NCL FFT operation is 452 ns, which means it takes 452 ns to compute the final result after getting new data. When running at this speed, the average current, *Iavg*, flowing through the NCL FFT is 0.0267 A. Running the synchronous FFT at the same speed as the NCL version requires a clock frequency of 452/6 = 75.3 ns. The average current of the synchronous FFT is 0.0354 A at this speed. Therefore, the power consumption for the synchronous FFT is 33% higher than the NCL version running at the same speed. The highest clock speed to operate the synchronous FFT without any timing violation is 9.75 ns, resulting in a calculation time of 9.75\*6 = 58.5 ns to obtain the final result. At this fastest speed, the synchronous FFT requires 70% higher energy consumption than the NCL FFT and 28% more than when running it slower. Hence, although the NCL FFT is bigger and slower, it consumes less power than the synchronous FFT, even when operating at the same speed.

Table III. Comparison of NCL and synchronous FFT processor

|                 | Computation Time (ns) | $I_{avg}\left(A ight)$ | Energy(10 <sup>-9</sup> J) |

|-----------------|-----------------------|------------------------|----------------------------|

| NCL FFT         | 452                   | 0.0267                 | 14.49                      |

| Synchronous FFT | 452 = (75.3 * 6)      | 0.0354                 | 19.20                      |

| Synchronous FFT | 58.5 = (9.75 *6)      | 0.3500                 | 24.57                      |

#### REFERENCES

[1] Nasser Kehtarnavaz, Real-Time Digital Signal Processing: Based on the TMS320C6000, Newnes, 2004.

<sup>[2]</sup> Wayne T. Padgett, David V. Anderson and Jose Moura, Fixed-Point Signal Processing, Morgan and Claypool Publishers, 2009.

<sup>[3]</sup> R. Veenkant, "A serial minded FFT," Audio and Electroacoustics, IEEE Transactions on, vol. 20, pp. 180-185, 1972.

[4] Alan V. Oppenheim, Ronald W. Schafer and John R. Buck, Discrete-time signal processing, Prentice Hall, 1999.

[5] Sanjit Mitra, Digital signal processing A computer-based approach, McGraw-Hill Science/Engineering/Math, 2005.

[6] Scott C. Smith and Jia Di, Designing Asynchronous Circuits using NULL Convention Logic (NCL), Morgan & Claypool Publishers, July 2009.

[7] S. C. Smith, "Gate and throughput optimizations for null convention selftimed digital circuits," Ph.D dissertation, Dept. Computer Eng, Uinv.of Central Florida, Orlando, Florida 2001.

[8] K. M. Fant and S. A. Brandt, "NULL convention LogicTM: A complete and consistent logic for asynchronous digital circuit synthesis," in Proceedings of International Conference on Application Specific Systems, Architectures and Processors: ASAP '96, 1996, pp. 261-73.

[9] S. C. Smith, "Speedup of NULL convention digital circuits using NULL cycle reduction," J. Syst. Archit., vol. 52, pp. 411-22, 07, 2006.

[10] V. Satagopan, B. Bhaskaran, W. Al-Assadi, S. C. Smith and S. Kakarla, "DFT techniques and automation for asynchronous NULL conventional logic circuits," IEEE Transactions on very Large Scale Integration (VLSI) Systems, vol. 15, pp. 1155-9, 10, 2007.

[11] G. E. Sobelman and K. Fant, "CMOS circuit design of threshold gates with hysteresis," in ISCAS '98 Proceedings of the 1998 IEEE International Symposium on Circuits and Systems, 1998, pp. 61-4.

[12] S. C. Smith, R. F. DeMara, J. S. Yuan, D. Ferguson and D. Lamb, "Optimization of NULL convention self-timed circuits," Integration, the VLSI Journal, vol. 37, pp. 135-65, 08, 2004.

[13] S. C. Smith, R. F. DeMara, J. S. Yuan, M. Hagedorn and D. Ferguson, "Delay-insensitive gate-level pipelining," Integration, the VLSI Journal, vol. 30, pp. 103-31, 10, 2001.

[14] Behrooz Parhami, Computer arithmetic: Algorithms and hardware designs, Oxford University Press, New York, 2000.

[15] S. C. Smith, "Design of a NULL convention self-timed divider," in Proceedings of the International Conference on Embedded Systems and Applications ESA'04 - Proceedings of the International Conference on VLSI, VLSI'04, June 21, 2004 - June 24, 2004, pp. 447-453.

[16] W. Kuang, J. S. Yuan, R. F. DeMara, M. Hagedorn and K. Fant, "Performance analysis and optimisation of NCL self-timed rings," IEE Proceedings: Circuits, Devices and Systems, vol. 150, pp. 167-172, 2003.

# Network-Based System for Face Recognition on Mobile Wireless Devices

Keita Imaizumi and Vasily G. Moshnyaga Graduate School of Engineering, Faculty of Engineering Fukuoka University Fukuoka, 814-0180 Japan

*Abstract* - This paper describes new internet-based face recognition system to be used in portable devices. In contrast to existing systems, which run computationally intensive facerecognition tasks at a mobile terminal shortening its battery lifetime, the proposed system uses mobile device only for image capturing and user-interface. All complex image processing tasks are performed by a remote high-powered network server to achieve robust and real time face recognition. The system is implemented in software and tested on Android-based Sony Tablet-S wireless terminal. According to measurements, it provides face recognition in images of 240x320 pixels in size at 10f/sec rate with very high accuracy. The paper discusses the proposed client-server architecture and the results of its experimental evaluation.

Keywords- face recognition, face identification, network-based

#### I. INTRODUCTION

With emerging popularity of camera-equipped wireless multimedia devices, such as Apple's iPhone, iPad and iPod, Google's Android, and RIM's Blackberry, new applications employing face recognition can further enhance usage, intelligence and context-awareness of the devices. In this paper, we focus on real-time identification of a person from a digital image or video captured by the mobile device [1]. Providing a stand-alone mobile application can potentially benefit a user in remembering people, retrieving names of people, whom he/she has met before, and/or finding helpful information about person of interest. It could be also useful for elderly people to recall faces and names enhancing their memory and social interaction. The application can also assist law enforcement when an unknown person is being compared with images in a database in real time.

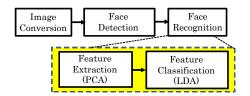

Automatic face recognition has been an active research area over the last two decades. Surveys on the methods and systems proposed can be found in [2], [3]. Although there are many systems capable of performing robust face recognition at desktops, incorporating them into mobile devices is not a trivial task. Additionally to common problems, such as face illumination, occlusion, rotation and movement of the person relatively to the camera, mobile face recognition is challenged by limited energy budget of batteries, limited computing power, limited storage, limited image resolution and size, limited network bandwidth, etc. Although it is easy for a human to detect and recognize faces, performing it on hardware requires complex algorithms and many energy dissipating computations. The high computational complexity of the task makes it unsuitable for energy and resource constrained mobile devices. While work has been done on algorithms which reduce the amount of computation for face detection and identification (e.g. a unified LDA/PCA algorithm [4], Haar-like Adabooth classifiers [5], geometric features [6], Local-Binary Pattern [7] and random incremental classifier [8], platform-driven mapping [9], etc.), there is an inherent tradeoff between computation and recognize faces accurately are extremely computationally complex, whereas computationally simple algorithms often produce incorrect results.

Several systems for mobile face recognition have been already reported in literature. Some of them (e.g. [6, 7, 8, 11, 12, 1]) utilize fast algorithms to run the face recognition process entirely on a mobile device at the cost of accuracy and operation time. The others, such as [13-15] overcome the performance limitations of mobile platforms through effective utilization of the network resources. Rather than implementing the whole face recognition process on the energy constrained mobile device, these systems transfer the majority of computation from the device to a high-powered server on the network. For example, the Bluetooth-based system [13] implements on mobile device image preprocessing and face detection while the face recognition is done on dedicated computer (server). Similarly, [14] and [15] use the DROID phone to detect a face in an image, preprocess the face calculating the Fisherfaces weights, based on which the server performs face recognition. However, even these distributed architectures still enforce mobile devices to carry out many computations, affecting both the battery budget and the processing speed. This is due to the lack of mobile processors (e.g. ARM) for executing floating point operations and also to the fact that face detection performs exhaustive image scans at different locations and scales, yielding in hundreds of thousands of sub-windows to process, which is time consuming. By tuning out the system parameters, one can further speed-up the detector but at the cost of quality degradation.

In this work, we also employ a network-based approach to reduce computation on mobile device. Unlike related systems, we use mobile device only as input and output interface; all functions of face detection and face recognition are done by the network server. The key contribution of our work is new clientserver architecture, which effectively utilizes the network as a powerful computational resource to achieve face recognition at a frame rate.

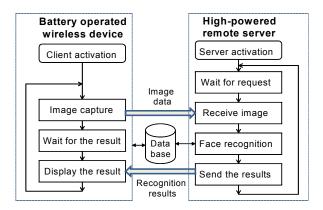

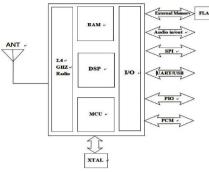

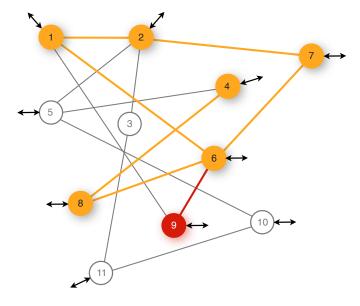

Figure 1: The face recognition flow in the proposed system

Figure 2: The face recognition tasks implemented by the server

The paper is organized as follows. Section 2 describes the proposed network-based face recognition system. Section 3 reports evaluation results. Section 4 summarizes our findings and outlines work for the future.

#### II. THE NETWORK-BASED FACE RECOGNITION SYSTEM

#### A. An overview

The proposed network-based face recognition system utilizes a high-powered remote server and a battery operated mobile wireless device (client), equipped with a video camera. The server has access to a face database which contains face images with corresponding information of the person. We assume that the database is shared between the client and the server through a cloud so the user has an option to upload new face images and add/delete data from database using either his/her mobile device (client) or the server (computer). Also we assume that the server is activated before the user initiates face recognition application from the wireless device. The client – server connection is set before entering the data transfer phase and released after data transmission is complete. The connection is established based on TCP/IP protocol and managed by OS through a programming interface.

The system splits the face recognition tasks between the client and the server, as shown in Fig.1. The server performs complex and accurate face recognition, while the client implements only I/O operations related to image acquisition and display of the results. The face recognition starts as the user activates the application from his/her mobile device. In this case, the client captures an image and sends it to the server with a request for processing. Upon receiving the request, the server converts image from YUV to RGB format and runs face detection and face recognition (see Fig.2) to identify the person

| Pixel[0] Pixel[1] Pixel[2] Pixel[3]                  | Pixel[0] Pixel[1] Pixel[2] Pixel[3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Y:Sbit<br>USbit<br>VSbit<br>VSbit<br>VSbit<br>VSbit  | B8bit<br>G8bit<br>R8bit<br>R8bit<br>R8bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VShit<br>YShit<br>Pxel[4] Pixel[5] Pixel[6] Pixel[7] | BSbit<br>GSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSbit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit<br>RSBit |

Figure 3: The image format used by the client (left) and the server (right)

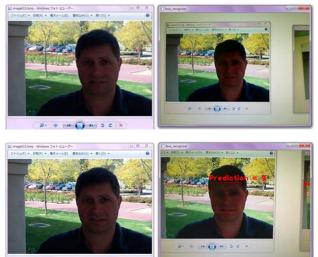

Figure 4: An illustration of an input image (a), the face detection result (b) and the result of face recognition (c)

of interest based on information stored in database. The results in terms of face rectangle and data identifying the person of interest are then sent back to the client, to be shown over the image displayed on the screen. In the next subsections we discuss the face recognition steps in details.

#### B. Image conversion

The color image captured by video camera on mobile device is represented in YUV 420 SP format, allowing reduced bandwidth for chrominance components. During transmission, the luma (Y) and the chroma (U and V) components are compressed with the sample ratio of 4:1:1 (see Fig.3); so the picture has only a quarter as much resolution in color as it does in brightness. Because the server uses RGB888 image format (Fig.3, right) for face recognition, each image is converted at the server from YUV to RGB format as follows:

$$B[i] = \{1192 \times (Y-16) + 2066 \times (U-128)$$

(1)

$$G[1] = \{1192 \times (Y-16) + 833 \times (V-128) - 400 \times (U-128)$$

(2)

$$R[i] = \{1192 \times (Y-16) + 1633 \times (V-128)$$

(3)

$$B = (B[i] >> 10) \& 0xFF$$

(4)

$$G = \{(G[i] >> 2) \& 0xFF(0) >> 8$$

(5)

$$R = \{ (G[1] >> 2) & 0xFF00 \} >> 16$$

(5)

$$((R[1] \times 0) \alpha 0 M 10000) > 10$$

(0)

#### C. Face detection

The goal of this task is to find an area corresponding to human face in the given RGB image if any. It is implemented based on Viola-Jones algorithm [5], which transforms the RGB image into the integral image representation, and then scans it with detection window to compute Haar-like face features. The features are then applied to a cascade of 25 AdaBoost classifiers to find a true face from possible candidates. The algorithm is implemented in Intel's OpenCV as cvHaarDetectObjects() using the Android's Face Detector class [16]. This class provides information regarding all the faces found in an input bitmap image. The confidence factor (a number between 0 & 1) by which the face is identified, the distance between the eyes, position of midpoint between the eyes and the face's pose (rotation around X, Y, Z axis) are the

Figure 5: An illustration of face sample generation

extra details the class associates with each face. A face is considered detected if the confidence ratio is above 0.3. The result of face detection is presented by a face bounding box depicted over the input image as shown in Fig. 4(b). The derived face image is preprocessed to gray scale and histogram equalization to decrease the effects of illumination, subsampled to the database sample size and applied for face recognition. If no face is detected, the server terminates the recognition process, sending a corresponding acknowledge signal to the client.

#### D. Face recognition

Given a set of sample images labeled with the person identity (the set is stored in database) and the unlabeled face image  $(x_i)$ , (derived by face detection), the face recognition problem is to identify the name of the person in the test image. We solve the problem based on the Eigenface method [17,18] with Principle Component Analysis (PCA) for feature extraction and the Fisher's Linear Discriminant Analysis (LDA)[19] for feature reduction. Having a set of N face images,  $a_1, a_2, \dots, a_N$ , with each image belonging to one of C classes,  $A_1$ ,  $A_2, ..., A_C$ , the method calculates a mean face of each class  $\Phi_i = (1/n) \times \sum_{i=1}^{n} a_i$ , the total mean,  $\Phi = (1/C) \times \sum_{i=1}^{N} \Phi_i$ , and vectors,  $D_i = a_i - \Phi_i$ , which represent difference between the mean and the training face images. This covariance matrix  $M = \{D_1, D_2, \dots, D_C\}$  of the face images is then subjected to LDA to find a set  $V_o = \{v_1, v_2, ..., v_k\}$  of k orthogonal vectors (i.e. eigenvectors), corresponding to the k largest eigenvalues. The LDA takes advantage of the fact that the classes are linearly separable, selecting the projection in such a way that the ratio of the between the class scatter and the within class scatter is maximized. The within-class scatter,  $S_W$ , is defined as the mean of the co-variances of samples within all classes, i.e.  $S_W = l/C (\sum_i^C M_i \times M_i^T)$ . The between-class scatter is defined as the co-variance of data sets consisting of mean vectors of each class:  $S_B = \sum_{i}^{C} (\Phi_i \Phi) (\Phi_i \Phi)^{T}$ . With LDA the problem is reduced to finding such a projection  $V_o$  that maximizes the total scatter  $S_T = S_W + S_B$  of the data while minimizing the within scatter of the classes:

$$V_o = \arg \max_V (V \times S_T \times V^T) / (V \times S_W \times V^T) = [v_1 \ v_2 \dots v_k].$$

(7)

The problem is solved through transformations such as rotating and scaling the axes of tested image in different ways. Depending on the size of the data, the projection can be done onto to a lower or higher dimension. The computed eigenvector matrix  $V_o$  is then used for estimating the weights of projecting the target face  $x_i$  onto these eigenvectors. The weights are

Figure 6: Example face images from the database "Faces1999"

calculated as  $W = V_0^T(x_i - \Phi)$ . A class  $A_j$  with the minimum Euclidean distance of weights is selected. The data related to the class is sent to the client as a result. Fig.5 shows an example. If no match has been found for the given face, the system marks it as an "unknown".

#### E. Implementation

The proposed system has been implemented based on the Sony Tablet-S (1GHz ARM Cortex<sup>TM</sup>-A9 dual core CPU, 1GB RAM, 16GB internal storage, 9.4-inch display, Android<sup>TM</sup> 4.03 OS) as a client and DELL PC (Intel® Core<sup>TM</sup> i5 2.80GHz CPU, 4GB memory, MS Windows 7 OS) as a server. The application software was created by using the Microsoft Visual Studio 2010 (Eclipse 3.6) and the Android software development kit. The client-server communication was implemented through Internet Socket API (ws2\_32.lib) and TCP/IP transport protocol [20]. To support the OS-based control of the communication, a dedicated programming interface was also created. The face detection and face recognition software were programmed in C/C++ by using Intel's Open CV 2.4.2 library[21].

#### III. EXPERIMENTAL EVALUATION

A number of experiments were conducted to assess performance of the proposed system. The first group of experiments aimed at evaluating efficiency of face detection and face recognition software implemented on the server computer. The second group of experiment targeted performance evaluation of the entire system. Below we discuss the experiments in detail.

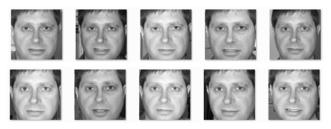

#### A. Evaluation of the face recognition software

To evaluate the ability of the developed face recognition software to detect and identify human faces correctly, we applied it to the "Faces 1999" database of 357 static frontal face images developed at Caltech [22] in total. For the sake of experiment, all the images have been manually transformed to grey-scale representation, resized and trimmed to face area only as shown in Fig.5. In such a way we prepared an experimental database of 17 different persons (9 men and 8 women), with each person represented by 10 images (170 images in total). Fig.6 exemplifies face images of the same person. All face images were 120x120 pixels in size and labeled by a unique digital tag for identification.

In the experiment, we used all 357 original pictures from Faces 1999 as an input to the developed face recognition software.

Figure 7: Example face images from the Face1999 database

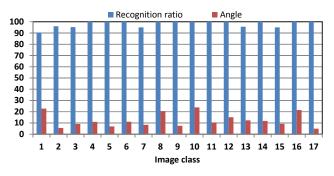

Figure 8: Recognition ratio and max.inclination angle per image

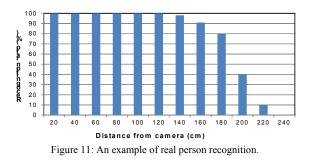

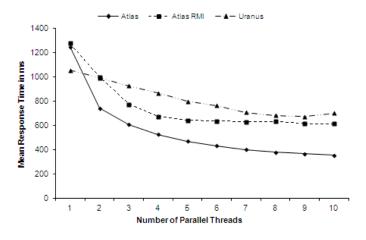

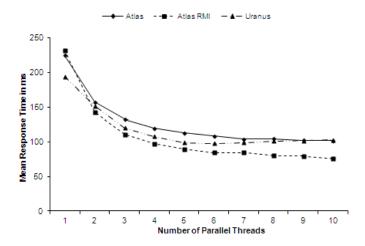

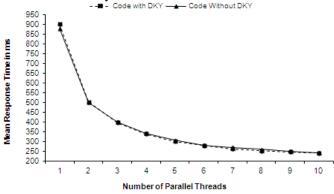

Namely, each image was captured by Logicool C600 video camera (640x480 frame size) from a display and used as an input image of a person to be identified. For each image we evaluated whether the face detection and face recognition produced correct or false results. To consider effects of face inclination, we repeated the test for each image by rotating the camera with  $5^{\circ}$  increment and determining the maximal inclination angle at which the results were correct. Fig.7 illustrates an image inclined by 25°.